+

+

+ Gate libraries:

@@ -142,7 +142,7 @@ QCA-STACK format, and to Sophia Kuhn for implementing the SVG writer!

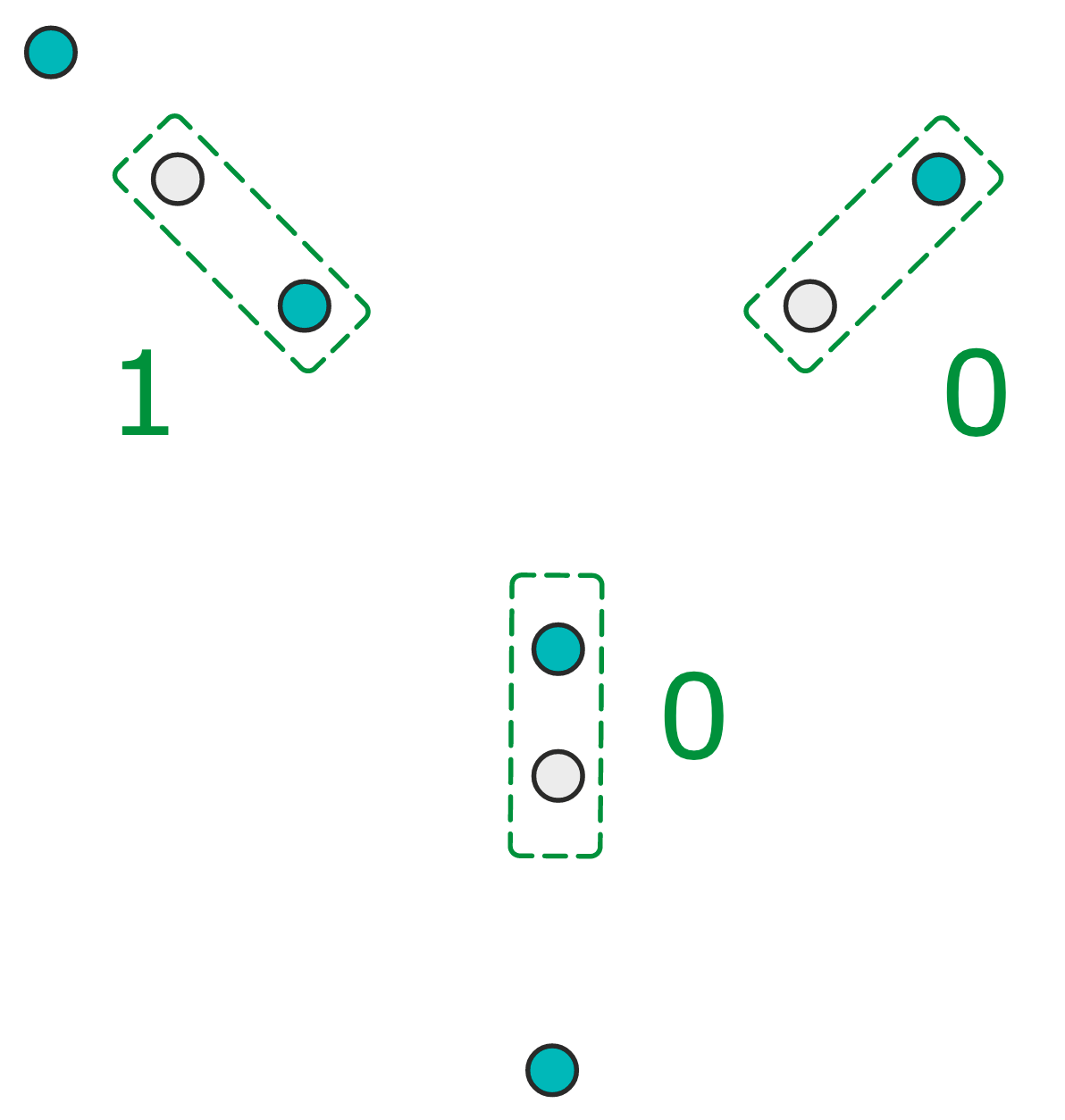

### in-plane Nanomagnet Logic (iNML)

-

Gate libraries:

@@ -142,7 +142,7 @@ QCA-STACK format, and to Sophia Kuhn for implementing the SVG writer!

### in-plane Nanomagnet Logic (iNML)

- +

+ Gate libraries:

@@ -157,7 +157,7 @@ Many thanks to Umberto Garlando, Fabrizio Riente, and Giuliana Beretta for their

### Silicon Dangling Bonds (SiDBs)

-

Gate libraries:

@@ -157,7 +157,7 @@ Many thanks to Umberto Garlando, Fabrizio Riente, and Giuliana Beretta for their

### Silicon Dangling Bonds (SiDBs)

- +

+ Gate libraries:

@@ -188,7 +188,7 @@ For automatic FCN layout obtainment, *fiction* provides algorithms that

receive [mockturtle logic networks](https://mockturtle.readthedocs.io/en/latest/implementations.html) as input

specification and output placed, routed, and clocked generic FCN circuits.

-

Gate libraries:

@@ -188,7 +188,7 @@ For automatic FCN layout obtainment, *fiction* provides algorithms that

receive [mockturtle logic networks](https://mockturtle.readthedocs.io/en/latest/implementations.html) as input

specification and output placed, routed, and clocked generic FCN circuits.

- +

+ Among these algorithms are

@@ -219,7 +219,7 @@ using

### Physical Simulation

-

Among these algorithms are

@@ -219,7 +219,7 @@ using

### Physical Simulation

- +

+ When a layout is compiled to the cell level via the application of a technology-dependent gate library, it can be

simulated using a physical model. Currently, the following simulation algorithms are implemented in *fiction*:

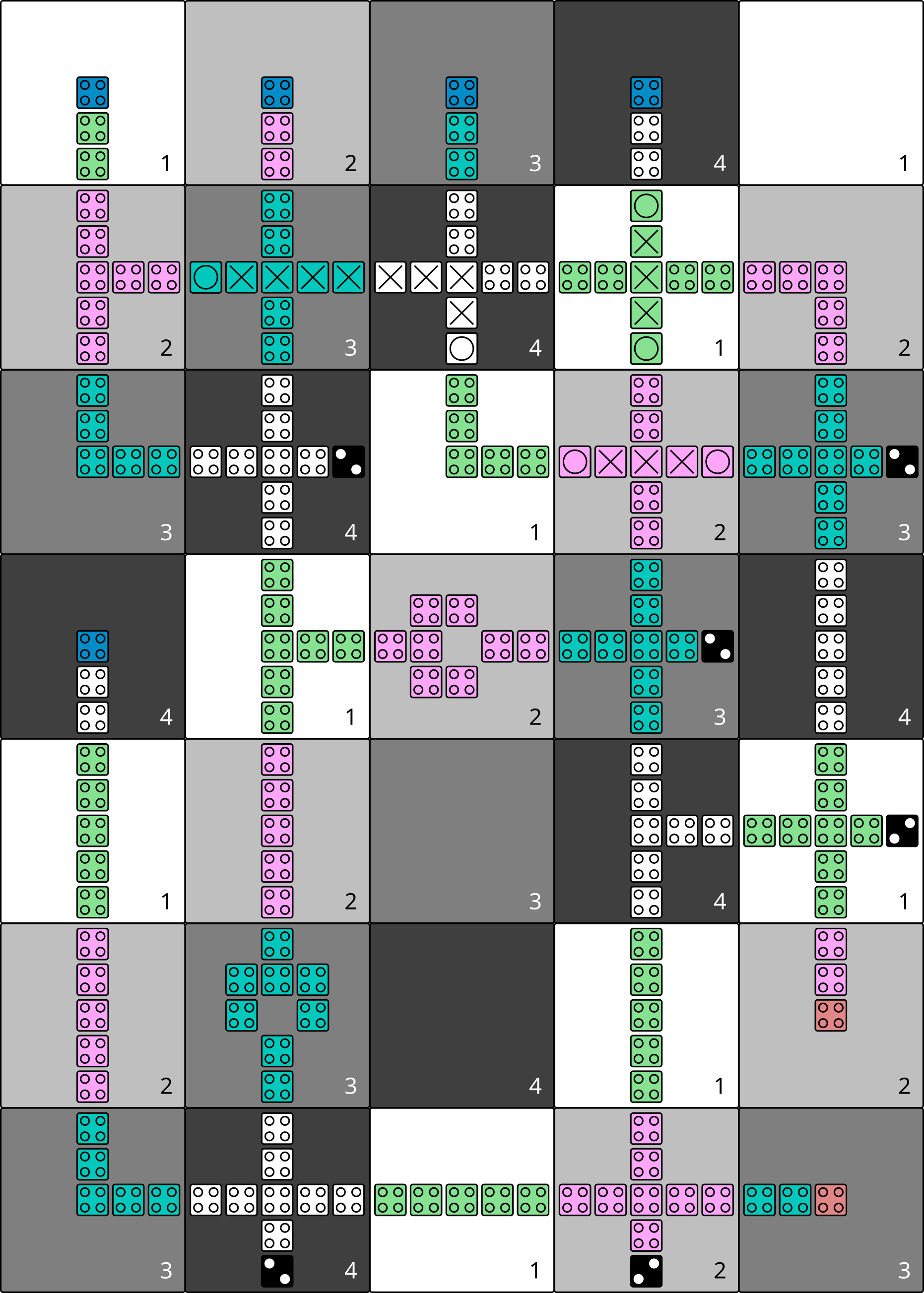

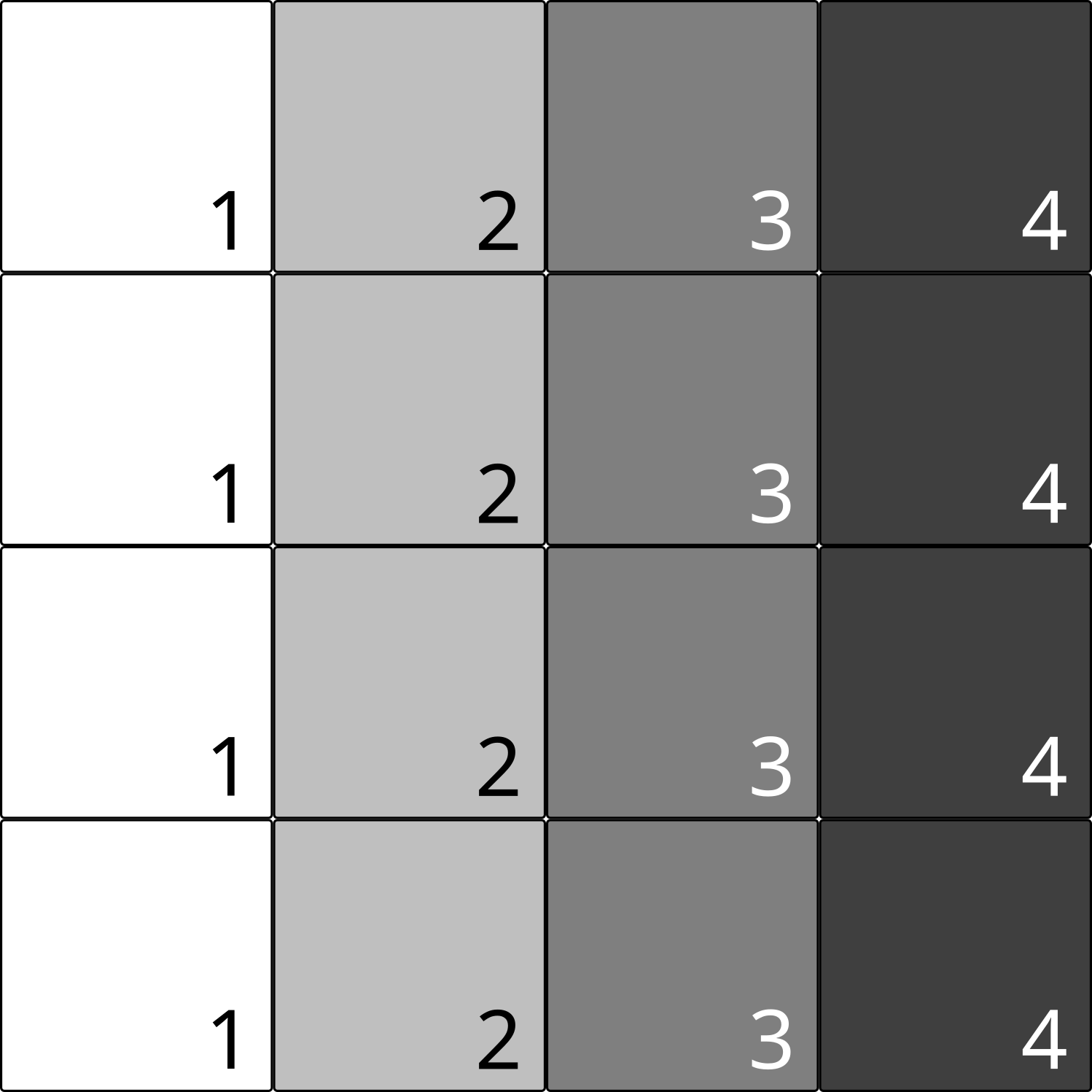

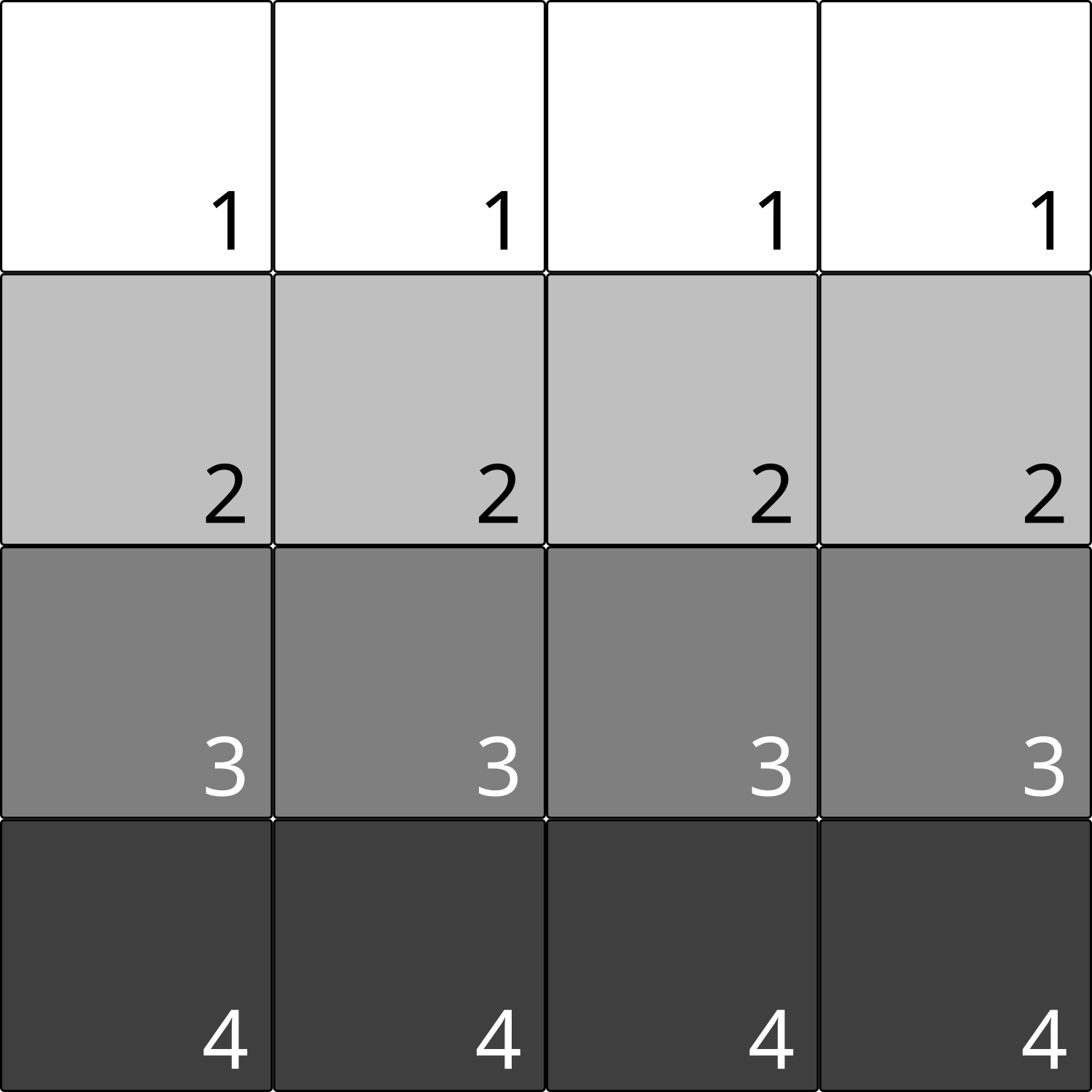

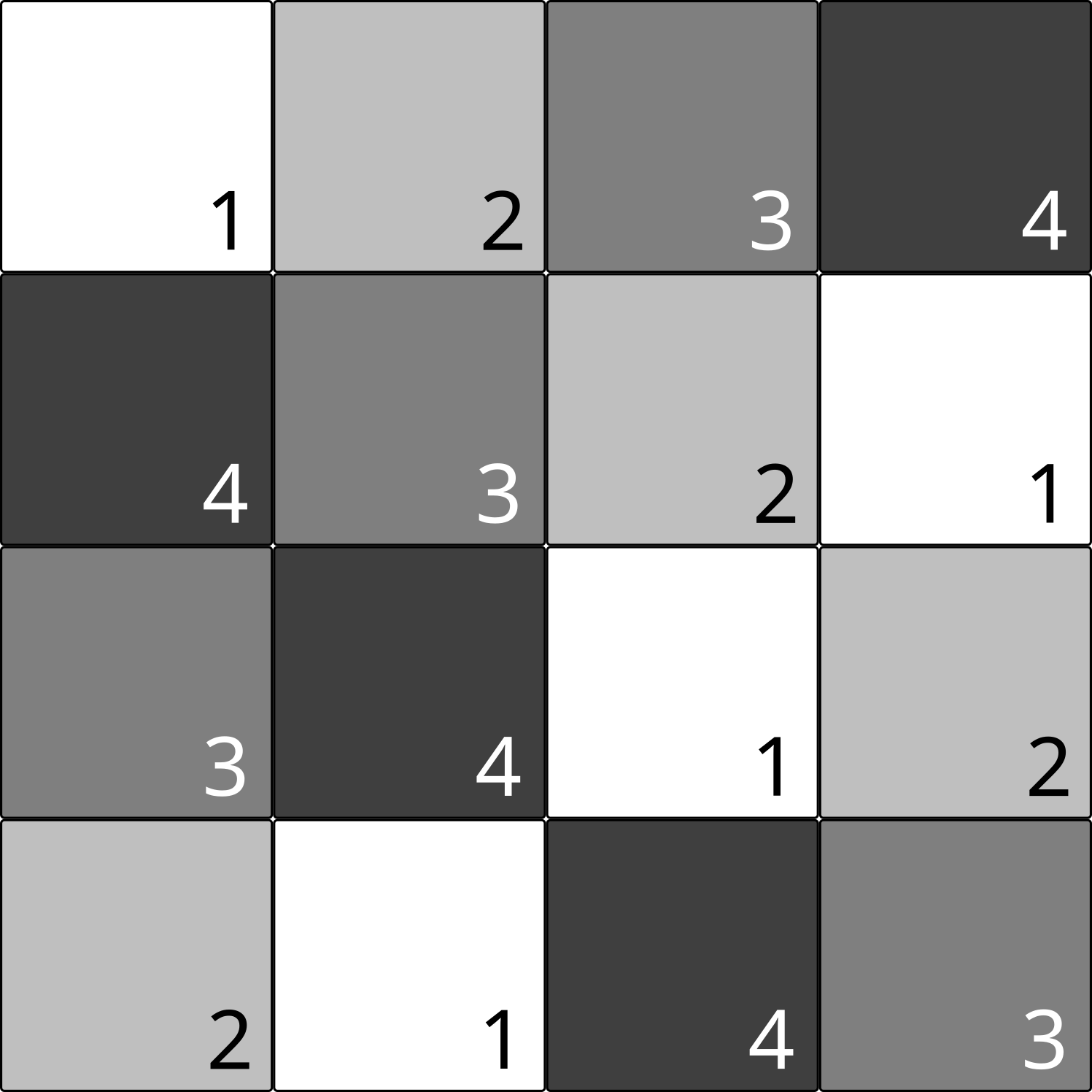

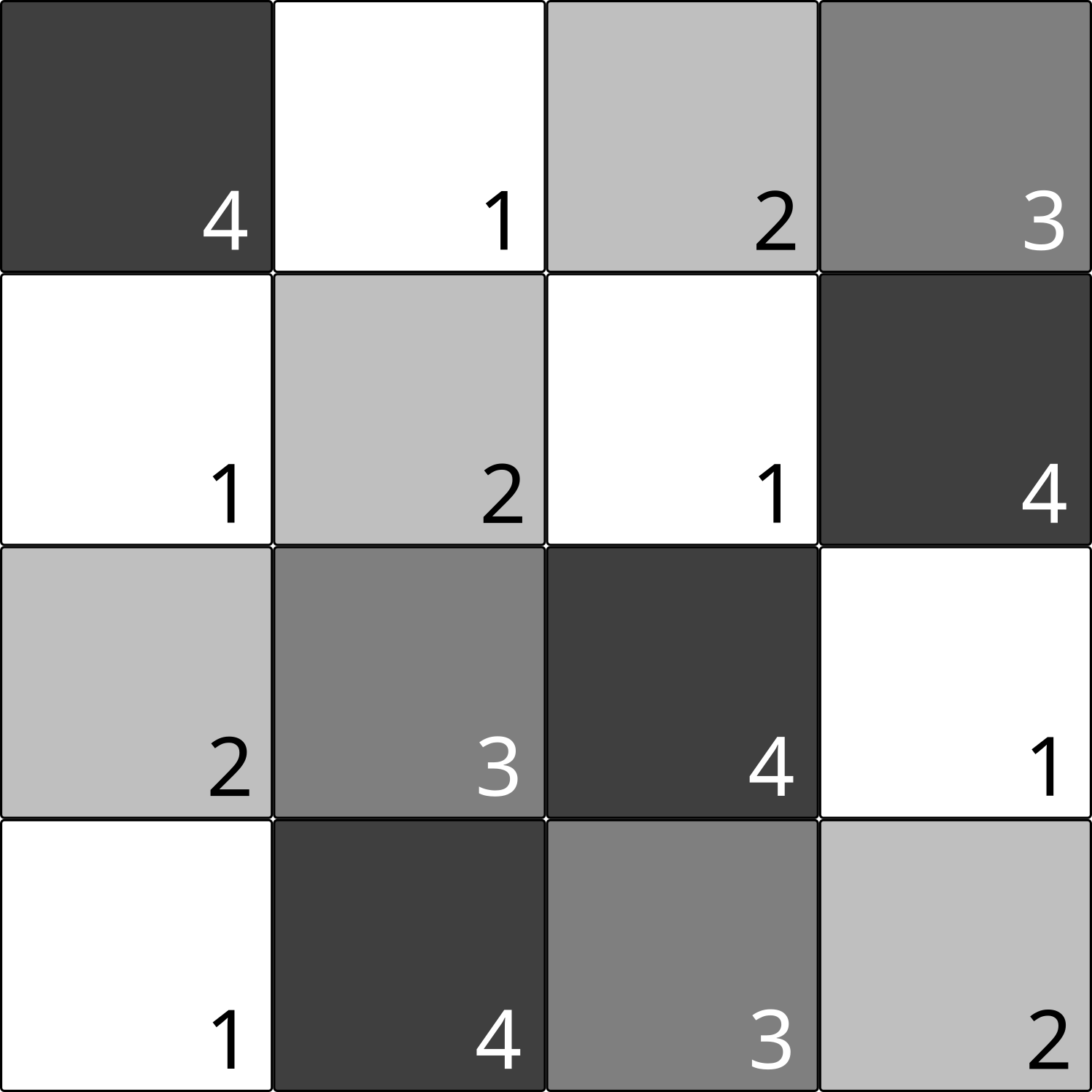

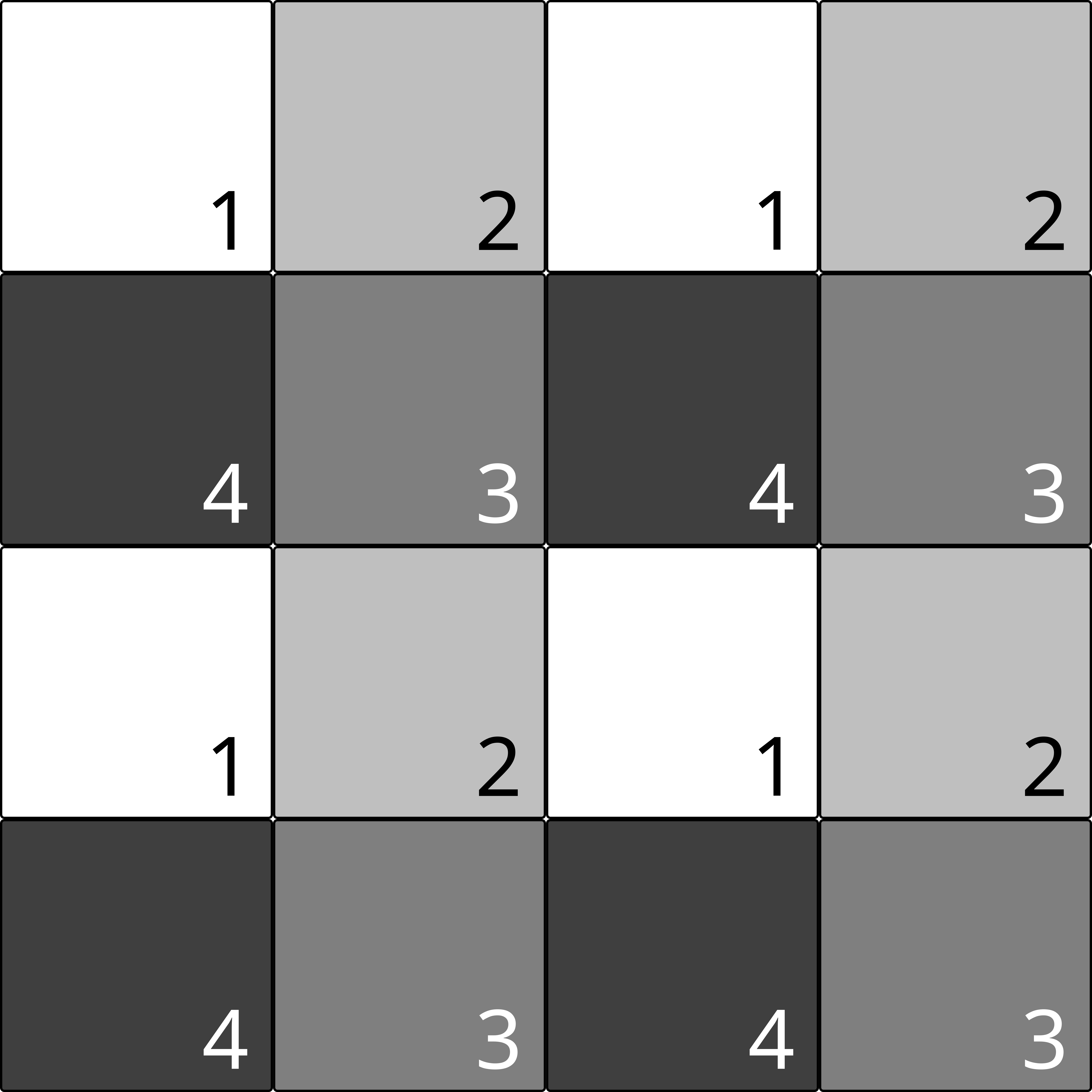

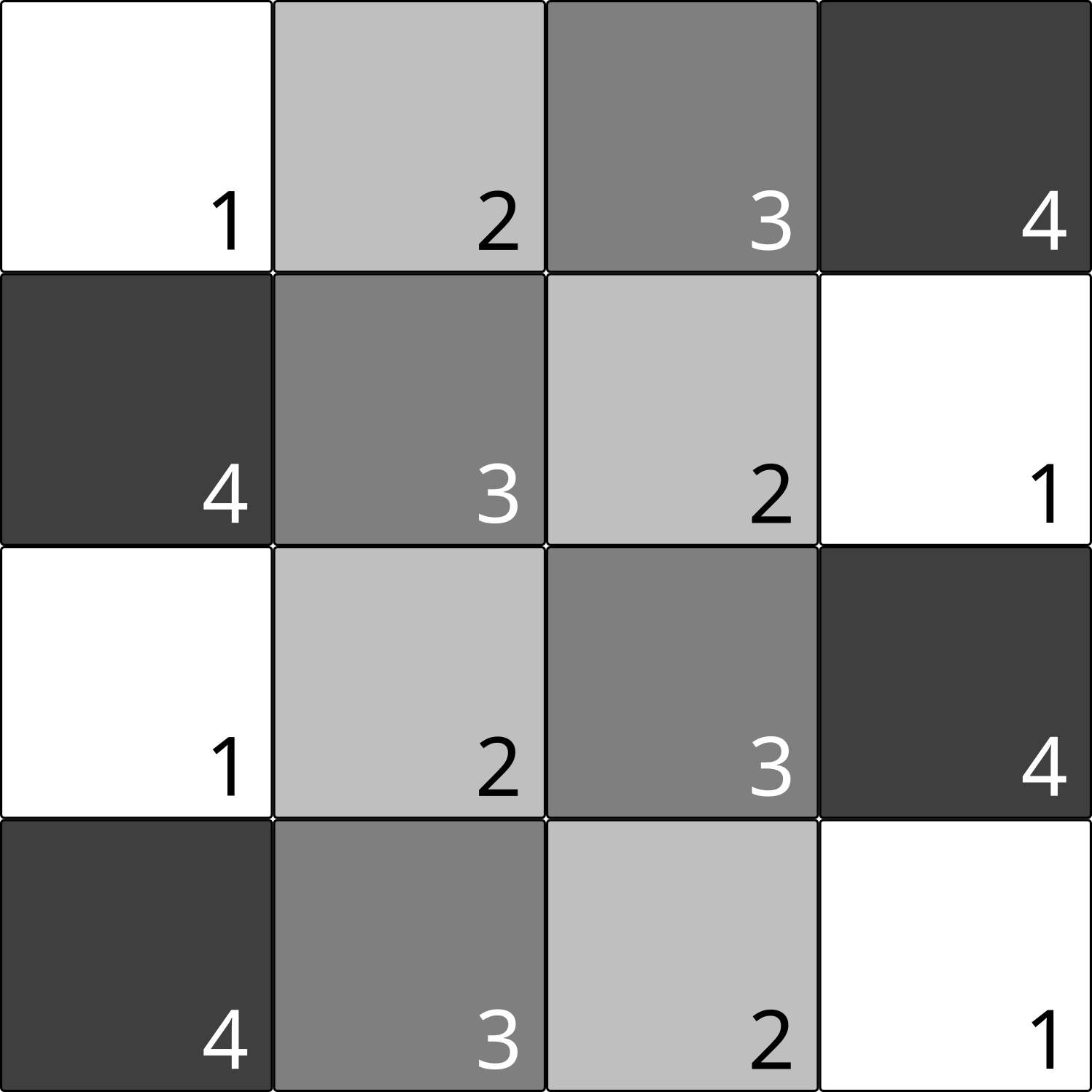

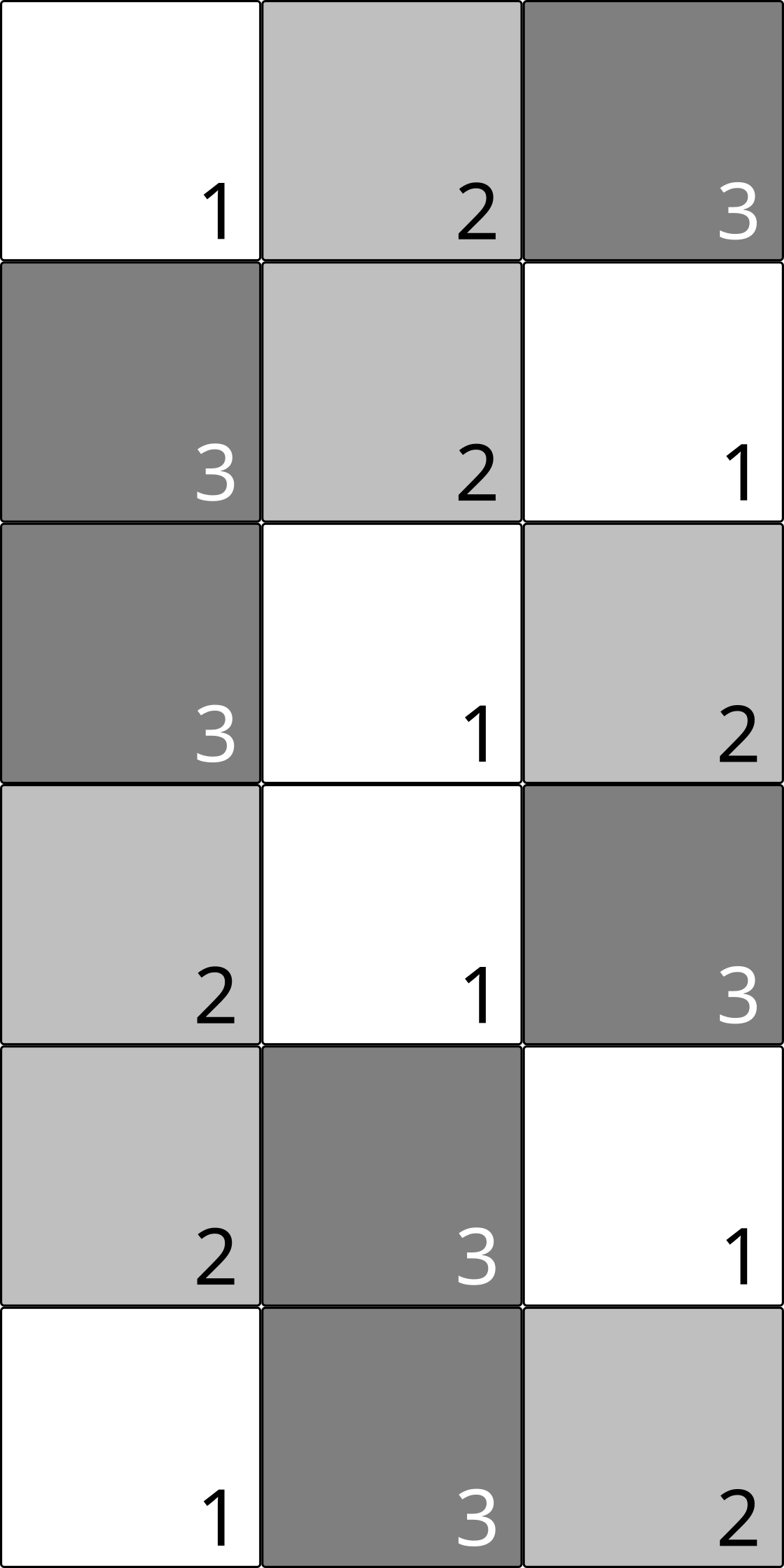

@@ -244,21 +244,21 @@ Built-in schemes are

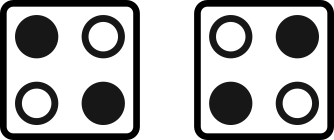

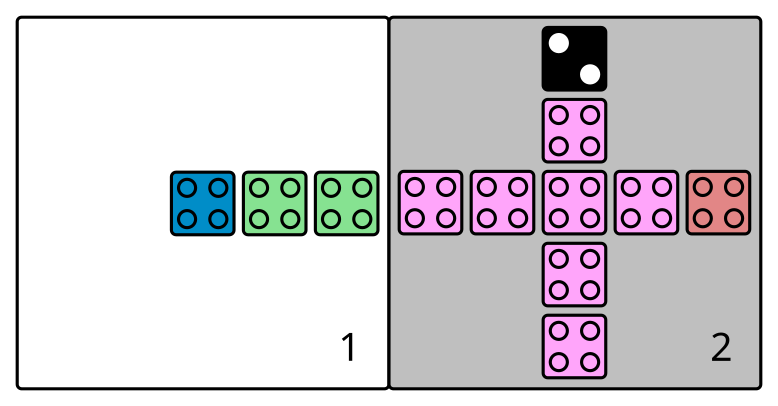

| [Columnar](https://ieeexplore.ieee.org/document/573740) | [Row](https://ieeexplore.ieee.org/document/573740) | [2DDWave](https://ieeexplore.ieee.org/document/1717097) |

|:------------------------------------------------------------------:|:--------------------------------------------------------:|:----------------------------------------------------------------:|

-|

When a layout is compiled to the cell level via the application of a technology-dependent gate library, it can be

simulated using a physical model. Currently, the following simulation algorithms are implemented in *fiction*:

@@ -244,21 +244,21 @@ Built-in schemes are

| [Columnar](https://ieeexplore.ieee.org/document/573740) | [Row](https://ieeexplore.ieee.org/document/573740) | [2DDWave](https://ieeexplore.ieee.org/document/1717097) |

|:------------------------------------------------------------------:|:--------------------------------------------------------:|:----------------------------------------------------------------:|

-|  |

|  |

|  |

+|

|

+|  |

|  |

|  |

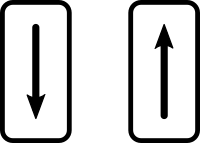

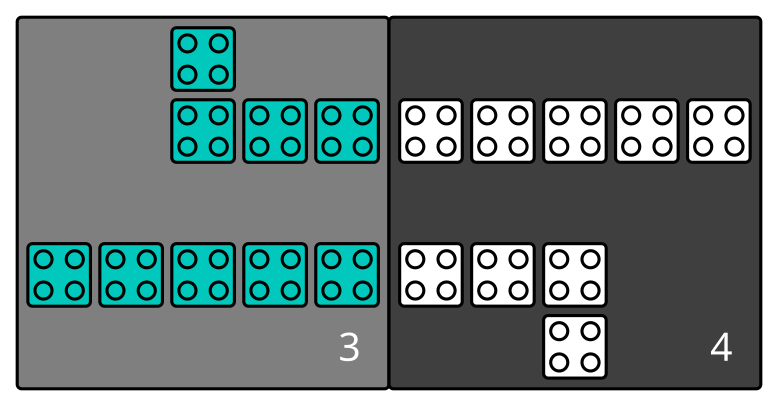

| [USE](https://ieeexplore.ieee.org/document/7219390) | [RES](https://www.tandfonline.com/doi/abs/10.1080/21681724.2019.1570551) | [ESR](https://link.springer.com/content/pdf/10.1007/s10470-020-01760-4.pdf) |

|:--------------------------------------------------------:|:------------------------------------------------------------------------:|:---------------------------------------------------------------------------:|

-|

|

| [USE](https://ieeexplore.ieee.org/document/7219390) | [RES](https://www.tandfonline.com/doi/abs/10.1080/21681724.2019.1570551) | [ESR](https://link.springer.com/content/pdf/10.1007/s10470-020-01760-4.pdf) |

|:--------------------------------------------------------:|:------------------------------------------------------------------------:|:---------------------------------------------------------------------------:|

-|  |

|  |

|  |

+|

|

+|  |

|  |

|  |

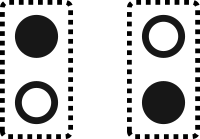

| [CFE](https://ietresearch.onlinelibrary.wiley.com/doi/10.1049/iet-cds.2019.0096) | [Ripple](https://scholarworks.rit.edu/cgi/viewcontent.cgi?referer=&httpsredir=1&article=8266&context=theses) | [BANCS](https://ieeexplore.ieee.org/document/8533251) |

|:--------------------------------------------------------------------------------:|:------------------------------------------------------------------------------------------------------------:|:------------------------------------------------------------:|

-|

|

| [CFE](https://ietresearch.onlinelibrary.wiley.com/doi/10.1049/iet-cds.2019.0096) | [Ripple](https://scholarworks.rit.edu/cgi/viewcontent.cgi?referer=&httpsredir=1&article=8266&context=theses) | [BANCS](https://ieeexplore.ieee.org/document/8533251) |

|:--------------------------------------------------------------------------------:|:------------------------------------------------------------------------------------------------------------:|:------------------------------------------------------------:|

-|  |

|  |

|  |

+|

|

+|  |

|  |

|  |

plus the mentioned irregular open clocking that works via a clock map instead of a regular extrapolated cutout.

## Wire Crossings

-

|

plus the mentioned irregular open clocking that works via a clock map instead of a regular extrapolated cutout.

## Wire Crossings

- +

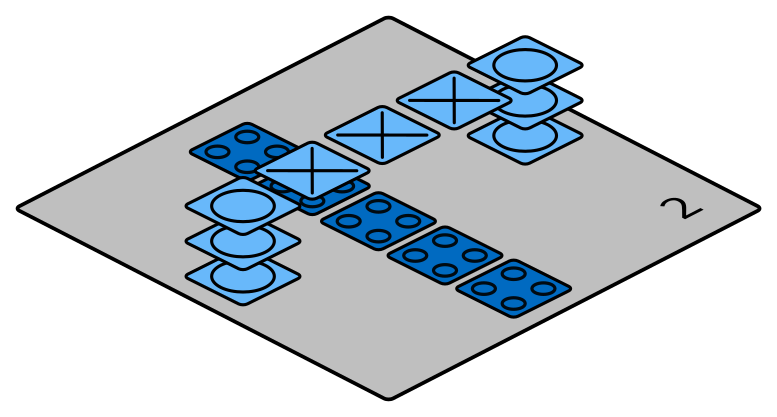

+ With many FCN technologies considered planar, wire crossings should be minimized if possible. However, there are some

options in QCA where, using a second layer, crossings over short distances and co-planar rotated cells become possible.

@@ -271,7 +271,7 @@ Wires are only allowed to cross other wires! Wires crossing gates is considered

## Gate Pins vs. Designated I/Os

-

With many FCN technologies considered planar, wire crossings should be minimized if possible. However, there are some

options in QCA where, using a second layer, crossings over short distances and co-planar rotated cells become possible.

@@ -271,7 +271,7 @@ Wires are only allowed to cross other wires! Wires crossing gates is considered

## Gate Pins vs. Designated I/Os

- +

+ In the literature, both are seen: having input cells (pins) directly located in the gate structure or using designated

I/O elements that are located outside of gates. This distinction only makes sense on the gate level and *fiction*

@@ -279,7 +279,7 @@ supports both approaches and offers usage in the implemented physical design alg

## Multi Wires

-

In the literature, both are seen: having input cells (pins) directly located in the gate structure or using designated

I/O elements that are located outside of gates. This distinction only makes sense on the gate level and *fiction*

@@ -279,7 +279,7 @@ supports both approaches and offers usage in the implemented physical design alg

## Multi Wires

- +

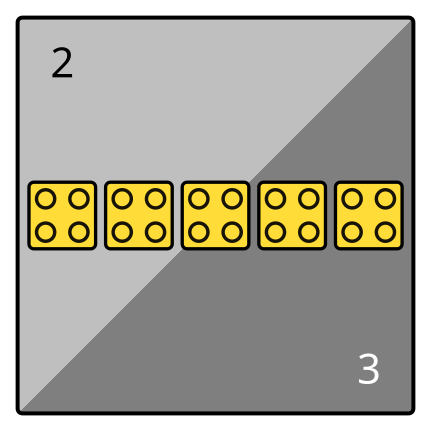

+ Gate-level abstraction has its limits. Often, chip area is wasted when only using a single wire per tile. In *fiction*,

cell-level layouts allow for precise control over cell placement and can, thus, also create multiple wire segments per

@@ -288,7 +288,7 @@ functionality.

## Synchronization Elements

-

Gate-level abstraction has its limits. Often, chip area is wasted when only using a single wire per tile. In *fiction*,

cell-level layouts allow for precise control over cell placement and can, thus, also create multiple wire segments per

@@ -288,7 +288,7 @@ functionality.

## Synchronization Elements

- +

+ A technology extension proposes to utilize the external clock signal generator in an unconventional way: by creating

further asymmetric clock signals with extended *Hold* phases that are assigned to specific wire

A technology extension proposes to utilize the external clock signal generator in an unconventional way: by creating

further asymmetric clock signals with extended *Hold* phases that are assigned to specific wire